内存层次设计

目录

题记

个人觉得计算机体系结构的内容很散,这里就随便记录一些上课内容.

Point

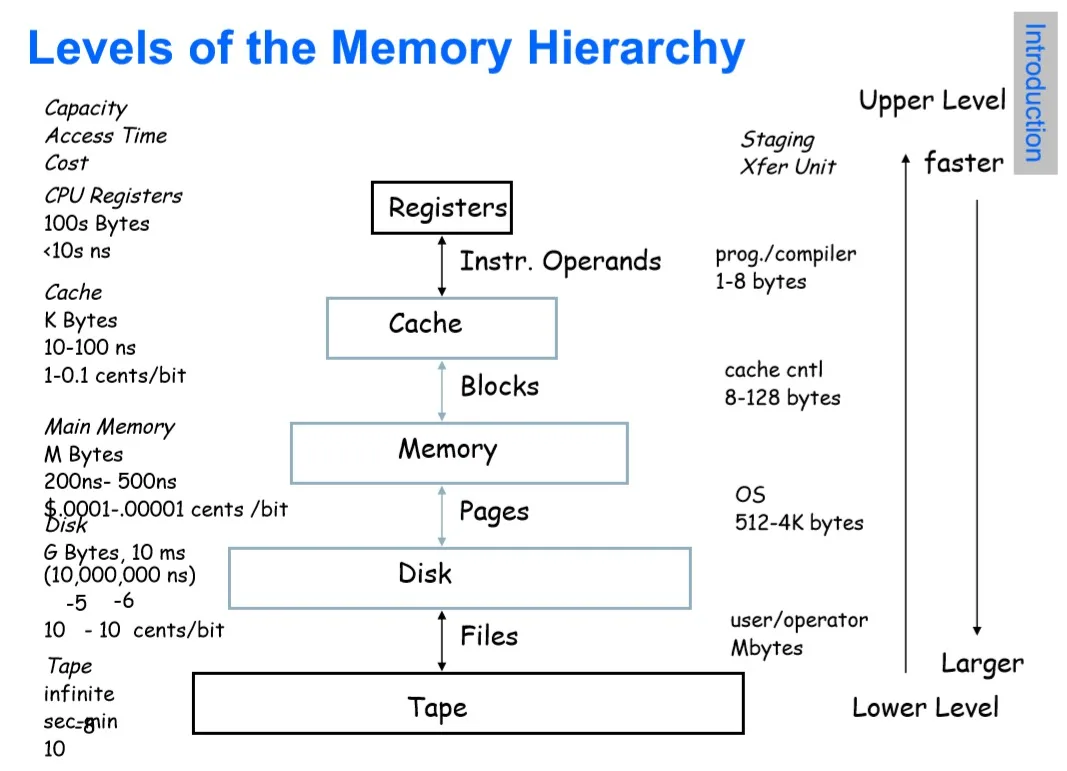

- 现在cpu处理器的速度已经超过内存。多核处理器也加剧了内存的压力.

- 因为disk读取速度慢,所以页的大小要比块的大小大很多.

- 寄存器由编译器来管理。如c=a+b,编译器来分配地址,add $1,$2,$3.

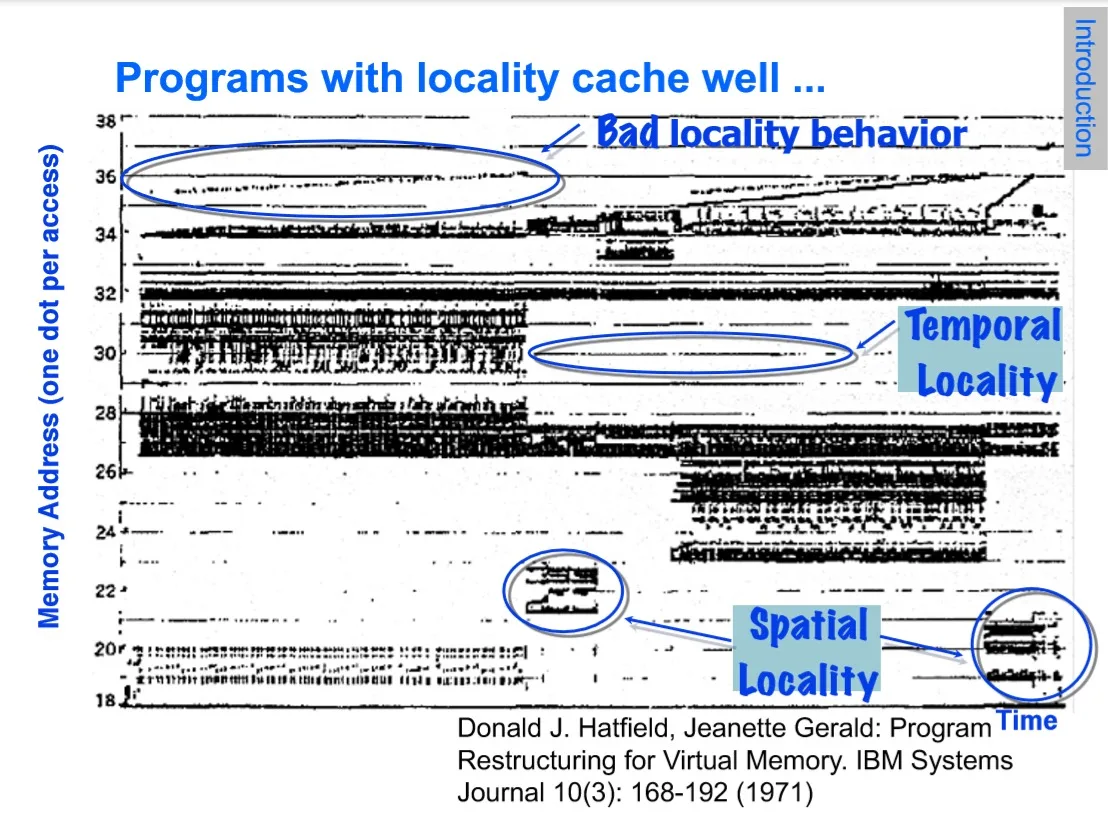

- Hit rate(在内存中找数据,能够在上层存储中找到的比率;即cache/(cache+memory))5和Hit time(RAM access time+Time to determine hit/miss)

- Miss penalty: time to replace a block from lower level, including time to replace in CPU

- 在单CPU串行的情况下,Average memory access time=Hit time + Miss rate * Miss penalty. 在多线程等情况下由多种优化策略,降低Miss penalty对速度的影响,而不简单是这个公式.

- 虚拟地址空间被分块,每一块称之为

页(page),页表(page table)可以通过虚拟地址索引,页表用于从virtual page numbes映射到physical frames.

参考资料

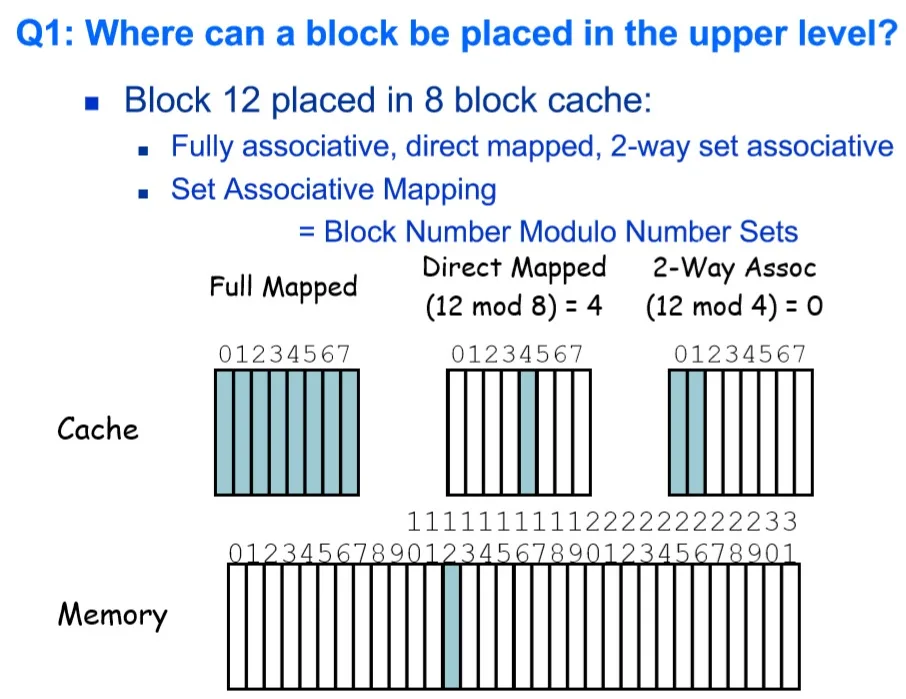

主存到Cache直接映射、全相联映射和组相联映射 https://blog.csdn.net/dongyanxia1000/article/details/53392315